What is RISC-V?

When it comes to designing your own CPU core, you primarily need to get an open-source ISA (instruction set architecture). This open-source ISA will help the CPU understand the programs and execute them accordingly. Most of us have worked with Intel’s x86 ISA, which is not only proprietary but also a CISC (complex instruction set computer), limiting us to use it for our own design. With the increasing popularity of open-source ISAs that can be OpenPOWER or RISC-V, we seeing more people adopting the new RISC-V instruction set architecture because of the support from toolchain vendors to fabricate the chips. Originating from UC Berkeley in 2010, the RISC-V ISA is a lot different from the ARM in terms of the licensing and complexity involved. RISC-V is optimized to the level where the implementation varies from a microcontroller to supercomputers. Even though ARM is well established in the mobile phones and single-board computer (SBC) industries, it won’t take a long time to see RISC-V in the picture. These are some of the significant reasons why RISC-V is considered a threat to ARM architecture. If you are interested in the details of RISC-V ISA, stick around because this is what you want to get started on. Learn all about what RISC-V is and why it could surpass ARM!

What is RISC-V?

In simple words, the RISC-V (pronounced as “risk 5”) is an open-source new instruction set architecture that came into existence for research and educational purposes. However, with the quick adoption and support of the ecosystem, it has become one of the most adopted open ISAs. This open ISA is available to the community that plans to work on hardware implementation and not just simulation or binary translation. The RISC-V instruction set architecture comes with a base ISA, which can be used and customized for educational use. Still, the user can also add optional extensions to make the processor core more powerful.

When RISC-V came into existence, the main motive was to remove the complexity to design any processor core. This particular hardware implementation has now turned into a software-visible interface for a wide range of implementations. For RISC-V to become a universal ISA, it should be efficient for all microprocessor styles (in-order, out-of-order, decoupled) and suit all processor sizes. One of the best examples of this is the implementation of RISC-V in the small embedded controller to its adoption in supercomputers.

When we listen to RISC-V, we always think of an open-source processor core. But in actual terms, it is the description of how the processor design should work. It describes how the software communicates with the hardware processor, similar to other popular ISAs in the market.

Also, the main question is why RISC-V is getting traction. To understand this, we need to first analyze the market scenario. When we talk about other popular ISAs like x86 or ARM, the support and ecosystem are incredible, but the right to design processor cores is very limited due to its associated fees for use. This not only limits the options but also bonds the company to stick with the processors designed by ARM vendors without major upgrades. But with an open ISA like RISC-V, innovative processor companies can now build their own products based on RISC-V to give a massive boost to innovation in the embedded processor industry.

What is an Instruction Set?

Many times, people get confused between instruction set architecture and microarchitecture. In simple words, an instruction set is a vocabulary of a computer’s language that describes the design of a computer in terms of simple operations like arithmetic, logic instructions. It is the interface between the hardware and lowest-level software that has all the information to write a machine-level program. One of the important things for you to know is that if you are aware of any other instruction set architecture like MIPS, or even x86, it is very easy to understand any new ISA. This is because the basic operation of any computer performs and the principles behind the hardware always remain the same. The only difference in different ISAs in the market is the simplicity and ecosystem around it while designing any hardware.

When we talk about microarchitecture, it lies below the instruction set architecture, making it different from the ISA. According to GeeksforGeeks, “The Microarchitecture is more concerned with the lower-level implementation of how the instructions are going to be executed and deals with concepts like Instruction Pipelining, Branch Prediction, Out of Order Execution.”

One may ask, why do we need yet another ISA when we have several of them in the market already? The simple answer to this is that while developing an ISA, the goal is to make it simple to design the hardware and compile it with maximum performance while minimizing power and energy. When we hear RISC-V ISA, it generally means the base integer ISA with optional extensions. The base integer ISA has to be present in any and all implementations and is developed with a minimal set of instructions making it convenient to build customized processors around it.

With RISC-V, there are currently four base ISAs that are characterized by the width of the integer register and the corresponding size of the address, and by the number of integer registers. There are two primary base ISAs corresponding to the 32-bit and 64-bit address spaces: RV32I and RV64I. We also have a subset variant of RV32I that has half the number of integer registers designed for small microcontrollers: RV32E. There is also a scope of exploring 128-bit address space that is built upon RV64I. All the base ISAs mentioned have differentiating features that can be used for a particular use case. The primary reason to separate the base ISA is to optimize each base ISA without the need to support operations of the other base ISA. But when we talk about all the advantages of separating the base ISA, there are also some downsides to it. One of the major downsides of not treating the design as a single ISA is that it can complicate the hardware design.

What is RISC-V Actually Used for?

Since we have already seen what RISC-V is all about, now let’s take a look at the use case of this open but frozen ISA. With modular architecture, you only chose the required, optional extensions with the frozen base ISA (e.g., RV32I). Since you only take the extensions that are demanding for the particular application, it helps the design to be power-efficient and low-cost, which can be critical in remote and embedded applications.

Due to these positives, the RISC-V ISA is seen in a wide variety of applications, from the Internet of Things to automotive applications and even controllers like graphics. With modular architecture, you can now build a custom processor-specific for the application and the product. This has helped the manufacturers to design processors targeted towards cloud servers with applications dedicated to HPC. We are also looking at RISC-V into general purpose applications like laptops and desktops. For this, SiFive entered the market of creating a RISC-V ecosystem for Linux application development with their recently launched HiFive Unmatched board that came with integrated SiFive FU740 SoC.

Image Credit: SiFive

Image Credit: SiFive

We have seen several developments in the RISC-V ecosystem to design IP cores targeting machine learning, artificial intelligence, and deep learning. At the RISC-V Summit 2020, Esperanto announced the RISC-V based chip, ET-SoC-1, aimed at machine learning with nearly 1,100 low-power cores. Along with Esperanto, Semidynamic also released the AVISPADO 220 core that came with the highlighting feature of an energy-efficient SoC for machine learning applications.

RISC-V also has set foot in the HPC with a dedicated working group. Leaders from the HPC industry believe that it will be sooner rather than later that we would see RISC-V ISA to power one of the world’s powerful supercomputers, such as processors and accelerators. Primarily RISC-V gained a lot oftraction in embedded systems applications, but to support the RISC-V ISA with the required ecosystem for the HPC, there has to be some work done. To support this, the SIG-HPC works on aligning the RISC-V architecture for HPC use cases. Barcelona Supercomputing Center is home to the very first RISC-V-based supercomputer in collaboration with SiFive.

When we think of taking any ISA to a certain application where it is not primarily designed, then there are some efforts by the enthusiasts who work on the ISA to make it compliant with the desired specific application. Since no one earlier thought of bringing RISC-V to the market of GPUs where the commercials have been outperforming and surprising the users every time. A group of enthusiasts came together to build new instructions on the base ISA that will be called RV64X supporting vectors, transcendental math, pixel, and textures, and Z/Frame buffer operations.

Who would have thought of taking RISC-V into space? As part of the European Horizon 2020 programme, Thales, Cobham Gaisler, the Barcelona Supercomputer Centre, and FENtiss came together to start developing RISC-V multicore processor design for space and aerospace applications. With all these implementations, the future of RISC-V seems to be very bright in other industries, including defense system products.

RISC-V vs. ARM

When you hear about RISC-V, the first question asked is on what makes it different from ARM or even x86 architecture. The first thing we need to understand about RISC-V being open source doesn’t mean open-source processors but is an open-source specification. Like ARM and x86, even RISC-V processor cores can be commercially licensed cores. But when we compare RISC-V and x86, we are comparing RISC and CISC computing architecture which has been an issue of debate for decades. But this is not the case for RISC-V and ARM because both of these ISAs are based on CISC computing architecture.

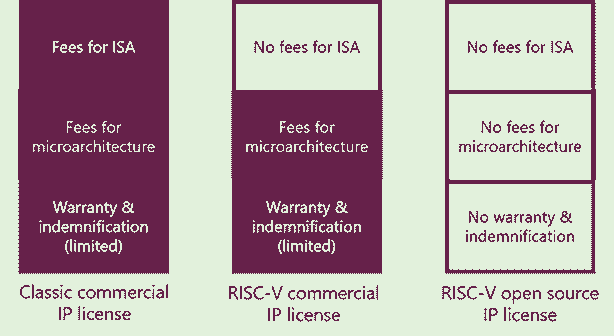

Image Credit: RISC-V International

Image Credit: RISC-V International

Even today, when we look at the mobile applications processors or even IoT device controllers, ARM has been dominating the market. One of the main reasons for this is the developed ecosystem and proven technology in a particular industry. When a new open-source ISA has to enter the market flooded by ARM products, it becomes difficult to make a difference. But as we have discussed, the upsides of the RISC-V architecture and growing adoption in a variety of industries have brought the ecosystem to a new height.

Some of the steps towards developing the ecosystem in a complex processor architecture started with the release of the SiFive HiFive Unmatched board. With such inventions and adoption, the software stack and other toolchains to support the level of applications have increased with due time. One of the other upsides for RISC-V is the standard extensions along with the frozen base ISA; we have not seen this in ARM. However, ARM has started to get in the optional extensions, which are helpful for a specific application processor.

In terms of a commercial IP license, the cost associated with the use of ISA is always high, and it comes with certain rules. This is one disadvantage with ARM that all chip manufacturers have to pay the fees to use the ARM ISA. With RISC-V, the chip manufacturer can directly manufacture its own processor cores, which can later be licensed for commercial use.

Which RISC-V Boards are Available?

Created in 2010, RISC-V remained mostly theoretical for many years until the development of the SiFive’s 32-bit Freedom Everywhere 310 SoC. This was the industry’s first available commercial SoC based on the open standard RISC-V architecture. With the release of this, the company released the first Arduino compatible HiFive1 development kit that was designed for microcontrollers, embedded, IoT, and wearable applications. However, the board was later discontinued and instead the HiFive1 Rev B was announced that came with the integrated FE310-G002 SoC, an upgraded version of the Freedom Everywhere SoC. But the FE310 SoC became so popular that we also saw many third-party developers and manufacturers crowdfunding and launching their development boards. Some of the other boards based on FE310 SoC include LoFive RISC-V SoC Evaluation Kit, SparkFun RED-V RedBoard, and SparkFun RED-V Thing.

Since the launch of the first SoC in the market, there has been a massive boost in the response from the community. This intrigued more third-party manufacturers to develop their own development boards based on the available commercial SoCs. Meanwhile, SiFive also came with the new SiFive 64-bit Linux-capable SoC platform called the HiFive Unleashed with Freedom U540 SoC supporting 8 GB DDR4 RAM.

As discussed, RISC-V can efficiently work on a variety of applications as there are several development boards for AI/ML workload and also IoT applications. But when we look at increased traction to open standard ISAs, there is a need to work in academia. To help students get started with RISC-V ISA, there are several boards designed by pioneering companies like the BBC that, in collaboration with Tynker and SiFive, launched an educational kit built around HiFive Learn Inventor hardware and RISC-V microcontroller.

If you are wondering, what about FPGA? Well, RISC-V has gotten into everything you can think of. The Microchip’s PolarFire SoC Icicle Kit is a low-power FPGA integrated with a 64-bit RISC-V microprocessor subsystem. It is primarily designed for applications in AI/ML, industrial automation, IoT, aerospace, and defense. As always, the RISC-V community doesn’t stop to surprise us. When we talk about RISC-V competing with other popular ISAs, one of the important things is to see the sustainability of RISC-V in mobile and computer processors. To start the era of RISC-V in personal computers, RISC-V adopted SiFive and released the first-ever RISC-V based PC with integrated Freedom U740.

For more information on the available RISC-V development boards, visit the RISC-V exchange page here.

What is the Future of RISC-V?

Significant developments in the RISC-V ecosystem give us a sense of its fast-growing open-standard ISA. We have seen several other open-source ISAs earlier, but none of them got as much traction as RISC-V in all the major end applications. According to Semico’s survey, there will be 62.4 billion RISC-V CPU cores sold in 2025, with the ecosystem becoming robust and mature for the market.

For RISC-V, threatening the growth of ARM has become an obvious reason for several developments in the computer architecture industry. With the increasing tractions, it won’t be surprising to see ARM re-examine its market strategy. One of the interesting things about RISC-V adoption is the new startups that can now build their own IP cores without paying any fees associated with the ISAs. This gives the manufacturer and consumer the choice to choose from the available IP cores for this particular application.

The future of RISC-V is bright due to its adoption by the corporates and support in academia by the member universities. Commercial IP cores based on the RISC-V ISA have broken the duopoly of ARM and x86 that has captured the market, giving the users the advantage to collaborate and innovate. In recent years, we have already seen disruption in the semiconductor industry due to the growing RISC-V adoption by the corporates and makers community. It will only be a matter of time before we see RISC-V becoming the most powerful ISA in all sectors, given the tough competition from market leaders changing the computing world.

What is RISC-V and Why Should You Care - RISC-V Explained

In the end, note that RISC-V is not an open processor core, but it is an open standard specification that can be adopted by anyone free of cost. You can now build your own processor core based on RISC-V and can also commercially license IP cores with the minimal cost associated with it. The growing support of toolchains and software stacks is reducing the risk of using RISC-V ISA.

Open standard ISA offers the flexibility, customization ability, and collaboration around the world to solve the problems faced by a new ISA. There are several working groups with RISC-V International that deal with various aspects of RISC-V implementation, let that be HPC or security. You can now become a RISC-V individual member free of cost and can also join these SIGs. RISC-V is on its way to revolutionizing the computing world.

Leave your feedback...